2007 IEEE NSREC Short Course

# Section IV

## **Radiation Hardening at the System Level**

Ray Ladbury NASA Goddard Space Flight Center

## **Radiation Hardening at the System Level**

Ray Ladbury NASA Goddard Space Flight Center Radiation Effects and Analysis Group

### **Table of Contents**

| 1 | INTR  | ODUCTION: SYSTEMS AND SYSTEM HARDENING               | 3  |

|---|-------|------------------------------------------------------|----|

|   | 1.1 S | System-Level Mitigation: Why Now?                    | 6  |

|   | 1.2 0 | OVERVIEW OF THE SYSTEM-LEVEL HARDENING PROCESS       | 8  |

| 2 | WHE   | N DO WE MITIGATE?                                    | 13 |

|   | 2.1 F | REQUIREMENTS GENERATION AND FLOWDOWN                 | 13 |

|   | 2.2 F | RADIATION TESTING AND ANALYSIS: ERRORS AND INFERENCE | 15 |

|   | 2.2.1 | Errors and inference for TID                         | 15 |

|   | 2.2.2 | Errors and Inference for Displacement Damage         | 19 |

|   | 2.2.3 | Errors and Inference for SEE                         | 20 |

|   | 2.3 F | FAILURE COST AND SEVERITY                            | 22 |

|   | 2.4 F | FAILURE RISK AND CRITICALITY                         | 24 |

| 3 | RAD   | IATION EFFECTS AND THEIR MITIGATION                  | 28 |

|   | 3.1 F | RADIATION EFFECTS AND THEIR CONSEQUENCES             | 30 |

|   | 3.2 I | Destructive Single-Event Effects                     | 30 |

|   | 3.2.1 | Single-event latchup (SEL)                           | 31 |

|   | 3.2.2 | Single-Event Burnout (SEB)                           | 34 |

|   | 3.2.3 | Single-Event Gate Rupture (SEGR)                     | 35 |

|   | 3.2.4 | Other Destructive SEE                                | 36 |

|   | 3.3 N | Nondestructive SEE                                   | 38 |

|   | 3.3.1 | Single-Event Transients (SET)                        | 38 |

|   | 3.3.2 | Single-event Upset (SEU)                             | 40 |

|   | 3.3.3 | Multi-Cell and Multi-Bit Upsets (MCU and MBU)        | 40 |

|   | 3.3.4 | Single-Event Functional Interrupt (SEFI)             | 42 |

|   | 3.4 I | DEGRADATION MECHANISMS                               | 43 |

|   | 3.4.1 | Total-Ionizing Dose (TID)                            | 44 |

|   | 3.4.2 | Displacement Damage (DD)                             | 45 |

| 4 | MIT   | IGATION STRATEGIES                                       | 48 |

|---|-------|----------------------------------------------------------|----|

|   | 4.1   | MITIGATION FOR DESTRUCTIVE SEE                           | 50 |

|   | 4.1.1 | Threat Reduction                                         | 50 |

|   | 4.1.2 | Event Detection and Protection                           | 51 |

|   | 4.1.3 | Cold Sparing                                             | 52 |

|   | 4.2   | HARDENING TECHNIQUES FOR NONDESTRUCTIVE SEE              | 53 |

|   | 4.2.1 | Hardening for SEFIs                                      | 53 |

|   | 4.2.2 | Mitigation for SEUs, MBUs and other data loss mechanisms | 54 |

|   | 4.2.3 | Mitigating Single-Event Transients                       | 60 |

|   | 4.3   | MITIGATION FOR DEGRADATION MECHANISMS                    | 62 |

|   | 4.4   | VALIDATION                                               | 65 |

| 5 | PUT   | TING HARDENING INTO PRACTICE: AN EXAMPLE                 | 66 |

|   | 5.1   | Destructive SEL and Latent Damage                        | 67 |

|   | 5.2   | TID AND RLAT                                             | 68 |

|   | 5.3   | STUCK BITS                                               | 68 |

|   | 5.4   | INFORMATION LOSS: NONDESTRUCTIVE SEL, SEFI, MBU AND SEU  | 68 |

|   | 5.5   | SUMMARY                                                  | 71 |

| 6 | WHI   | EN MITIGATION BREAKS DOWN                                | 73 |

|   | 6.1   | BREAKDOWN OF ASSUMPTIONS                                 | 74 |

|   | 6.2   | Test Fidelity                                            | 76 |

|   | 6.3   | ENSURING REPRESENTATIVE TEST SAMPLES                     | 77 |

|   | 6.4   | Synergistic Effects                                      | 79 |

|   | 6.5   | COST-EFFECTIVE RISK REDUCTION                            | 79 |

|   | 6.6   | SUMMARY                                                  | 80 |

| 7 | CON   | CLUSION: CASE STUDIES                                    | 82 |

|   | 7.1   | SOLAR DYNAMICS OBSERVATORY (SDO)                         | 82 |

|   | 7.2   | EXPLORATION ROVERS: SPIRIT, OPPORTUNITY AND BEYOND       | 84 |

|   | 7.3   | SUMMARY                                                  | 86 |

| 8 | REF   | ERENCES                                                  | 88 |

#### **1** INTRODUCTION: SYSTEMS AND SYSTEM HARDENING

When I sat down to put this section of the course together, I discovered that no fewer than 15 past short-course sessions—dating all the way back to the first short course in 1980—have dealt with system-level approaches to radiation hardening and radiation hardness assurance (RHA). (See Table I). This remarkable—and frankly rather daunting fact—raises a number of questions, such as: "Why such an emphasis on the system level?" and "What is there left to cover?"

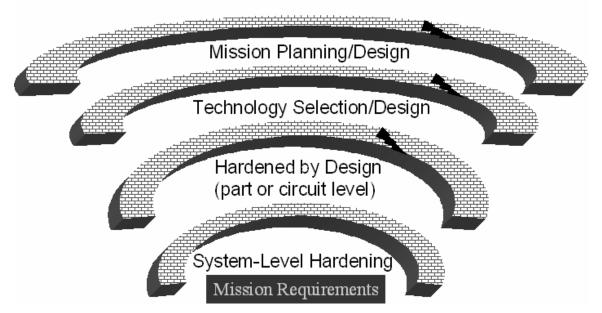

Part of the answer to the first of these questions is that the attention paid to the system perspective really does reflect the breadth of the topic. It has never been possible to fulfill all mission requirements solely using radiation hardened components—whether those components were vacuum tubes or the latest Radiation-Hardened-by-Design (RHBD) ASICs and Field-Programmable Gate Array (FPGA) designs. If the mission has a challenging radiation environment and requirements, and there is no radiation-hardened or RHBD solution, system-level hardening provides one last line of defense whereby a critical part with marginal radiation performance may still meet its system requirements. (See Figure 1-1.)

Another reason why system-level strategies are popular in short-courses is because system-level solutions tend to be rather involved and tailored to a particular system. As such, they often do not lend themselves to treatment in RHA literature for a general audience. System-level hardening becomes necessary only when a critical component has failed to satisfy requirements in traditional piece-part hardness assurance [1]. The process of mitigating the failure of a critical component can be complicated and expensive-both in terms of resources and system performance, giving rise to the conflicting demands of system-level hardening: The designer tells the radiation engineer, "Just make it work," while the program manager says, "Just make it cheap." Faced with such conflicting demands, the most efficient solution often winds up being application specific, providing just enough mitigation to meet requirements, and application specific solutions often do not lend themselves to publication in radiation-effects literature.

| Year | Author     | Title                                 | Emphasis                                                                         |

|------|------------|---------------------------------------|----------------------------------------------------------------------------------|

| 2004 | Lum        | Hardness Assurance for Space          | Overview of system hardness assurance from                                       |

|      |            | Systems                               | requirements to environments, device effects,                                    |

|      |            |                                       | mitigation and production                                                        |

| 2002 | Poivey     | Radiation Hardness Assurance for      | Overview of the usual hardness assurance                                         |

|      | 2          | Space Systems                         | program emphasizing requirements and parts                                       |

|      |            |                                       | qualification                                                                    |

| 1999 | Heidergott | System Level Mitigation Strategies    | Satellite constellations as a system;                                            |

|      | _          |                                       | environmental tradeoffs vs. constellation                                        |

|      |            |                                       | complexity; system-level consequences;                                           |

|      |            |                                       | commercial part qualification issues;                                            |

|      |            |                                       | mitigations and fault-tolerant systems                                           |

| 1998 | LaBel &    | Applying State of the art Commercial  | Roles and Limitations of state-of-the-art                                        |

|      | Cohn       | and Emerging Technologies to Space    | technologies to space systems; technology                                        |

|      |            | Systems                               | selection                                                                        |

| 1998 | Kinnison   | Achieving Reliable, Affordable        | Characterization and mitigation of radiation                                     |

|      |            | Systems                               | effects                                                                          |

| 1994 | Haddad &   | Adapting Commercial Electronics to    | Commercial part qualification strategies;                                        |

|      | Scott      | the Naturally Occurring Radiation     | mitigation and verification strategies; RHBD                                     |

|      |            | Environment                           | on commercial designs.                                                           |

| 1994 | Normand    | Single-Event Effects in Systems       | Environment, testing and statistical treatment                                   |

|      |            | Using Commercial Electronics in       | of SEE reflecting impact of application                                          |

|      |            | Harsh Environments                    | conditions.                                                                      |

| 1989 | Peden,     | Survivability and Hardening of Space  | strategic and natural environments with                                          |

|      | Josephson, | Systems (all 5 sections of the course | historical perspectives, environmental                                           |

|      | Ritter,    | deal with system level hardening)     | characteristics and specifics sections devoted                                   |

|      | Rudie,     |                                       | to history (Josephson), general techniques                                       |

|      | Swant,     |                                       | (Ritter), power (Rudie), Communications                                          |

|      | Abare and  |                                       | (Swant), Signal Data Processing (Abare) and                                      |

| 1005 | Price      |                                       | Payload (Price)                                                                  |

| 1987 | Robinson   | Packaging, Testing, and Hardness      | Outline of RHA process, especially                                               |

|      |            | Assurance                             | requirements, procurement, testing, analysis                                     |

| 1007 | D 1        |                                       | and oversight.                                                                   |

| 1986 | Raymond    | Subsystem Electronics Testing         | Approaches to testing and verification at the                                    |

|      |            |                                       | subsystem level; geared to strategic                                             |

|      |            |                                       | environments, but good insights for                                              |

| 1985 | Sievers &  | Fault-Tolerant Computing: An          | subsystem-level proton or TID tests.<br>Overview of fault-tolerant computing and |

| 1703 | Gilley     | Architectural Approach to Tolerating  | soft-error mitigation techniques                                                 |

|      | Onley      | Radiation Effects                     | solt-enor mitigation techniques                                                  |

| 1984 | Tasca,     | SGEMP Hardening of Spacecraft         | Requirements, mitigation and verification of                                     |

| 1904 | O'Donnell  | SOLIVIT Hardening of Spacecraft       | EMP hardening in electronic systems                                              |

|      | & Klisch   |                                       | Eivir hardening in electronic systems                                            |

| 1982 | Allen      | System Aspects of Radiation           | Hardening process from requirements to                                           |

|      |            | Hardening                             | design to productionstrategic                                                    |

| 1981 | Messenger  | Hardened Systems Development and      | Hardening systems for strategic                                                  |

|      |            | Hardness Assurance                    | environments                                                                     |

| 1980 | Johnston   | Radiation Effects on Components       | Device and circuit level effects, along with                                     |

|      |            | and Circuit Hardening                 | mitigations and component selection                                              |

| 1980 | Halpin     | System Effects and Systems            | Weapons effects and system-level validation                                      |

|      | 1          | Validation                            |                                                                                  |

| 1980 | Rudie      | System Hardening Methodology          | Nuclear hardness requirements, guidelines                                        |

|      | 1          |                                       | and planning                                                                     |

### Table I. NSREC Short Courses Dealing with System-Level Hardening

Similarly, journals, texts and handbooks on system engineering often give radiation issues a light treatment if they threat them at all. The short course offers a forum for indepth consideration of system-level hardening and for capturing the collected wisdom of the community when it comes to surmounting radiation threats.

## **Radiation Threats**

Figure 1-1. Radiation hardening can be viewed as a multi-tiered defense against radiation threat. The first line of defense uses mission planning and design to avoid unnecessary radiation risks. The second tier selects technology and designs the system so that components meet both mission and radiation requirements. Where there is no preexisting radiation hardened solution, hardness can be designed into the system at the part or circuit level. When a critical component appears questionable despite these measures, radiation hardening at the system level can help the component meet its system-level requirements.

As to what remains to be covered, the answer is: plenty. Many of the basic strategies of system-level hardening predate the space age, having been borrowed from communications and fault-tolerant computing. Still, although the basic strategies have not changed drastically since the first short course in 1980 (see the sessions by Alan Johnston, Joseph Halpin and Norman Rudie), every change in technology requires adjustments in how these strategies are applied. Each new project poses its own challenges, as demands for increased performance bend and then break formerly immutable rules (e.g. bans on commercial parts or parts susceptible to single-event latchup (SEL)). Moreover, the subject of system-level hardening is sufficiently rich and can be looked at from so many angles that it could probably become a yearly segment with little overlap year to year. Given the breadth of the topic we are grateful for the efforts of past presenters, which allow us to concentrate on some aspects of system-level hardening while directing the interested reader to past short courses for a more detailed treatment.

#### 1.1 System-Level Mitigation: Why Now?

In the vast majority of applications, the normal process of piece-part hardness assurance is sufficient to demonstrate that a part will meet its application radiation requirements. It is only when the piece-part process indicates that the part's radiation hardness is doubtful and when there is no good substitute part that system-level hardening may be necessary. In some cases, the mitigation required can be as simple as adding spot shielding to reduce TID or displacement damage dose (DDD), or adding capacitive filtering against single-event transients (SET). In other cases, it may involve an analysis to provide guidance to designers so that the system can accommodate parametric degradation or errors that are likely to occur. For very important enabling technologies, hardening may involve designing the entire system around the radiation vulnerabilities of a critical component. However, system-level hardening can be very expensive—in terms of project resources and also in terms of performance. As a result, most projects will not be able to afford more than a few such components, and the enhanced capability provided by the component will have to be worth the effort.

Usually, the components that provide such enhancements are commercial devices or other cutting (some would say bleeding) edge devices. Examples where commercial technologies provide sufficient performance to be tempting include:

Memories: The largest available single-die, radiation-hardened, volatile memories are the family of 16 Mbit SRAM from Aeroflex [2], while a variety of vendors offer 1Gbit DDR and DDR2 SDRAMs—a factor of >60 more density with comparable savings in weight, power and board area. For nonvolatile memory, the potential benefits are even greater, with FLASH memories having up to 4 Gbit of storage and radiation options for the foreseeable future being 4 Mbit or less. In terms of radiation performance, the price for this savings is a risk of destructive single-event latchup (SEL) and other destructive failure modes, a high rate of single-event functional interrupt (SEFI), the possibility of part-to-part and lot-to-lot variability in both TID and single-event effect (SEE) performance and the headaches of a short product lifecycle.

- 2) Processors The fastest radiation-hardened microprocessors execute a few hundred MIPS (for lack of a better accepted metric), while their commercial counterparts have execution speeds in the range of tens of thousands of MIPS. The main problems with commercial processors are that they tend to be susceptible to SEFI and for bulk CMOS, SEL. However, some missions and vendors have begun to look at system-level hardening approaches using commercial processors, in part taking advantage of the fact that some devices are manufactured in Silicon-on-Insulator (SOI) technology. [3], [4], [5]

- 3) Data Converters: Analog-to-Digital (A-to-D) and Digital-to-Analog (D-to-A) converters (ADC and DAC, respectively) are another area where radiation-hardened products lag the commercial sector. The highest resolution and highest speed radiation-hardened ADCs have 12-bit resolution and operate at 20 megasamples per second (MSPS),[6] while some commercial parts achieve 24-bit resolution, with 16-bit resolution being common. [7] Other commercial parts operate at 1 gigasample per second (GSPS) with 8-bit resolution. [8]. While most space applications do not require 16-bit resolution or GSPS speed, those that need it really need it, and have little alternative but to pursue a RHBD ASIC solution [9] or use a commercial offering. ASIC solutions are expensive, while commercial converters carry the risks of SEL, SEFI, TID degradation and high SET susceptibility.

- 4) Field-Programmable Gate Arrays: Radiation-hardened FPGAs have a long history of use in satellites, and have done a reasonable job pacing their commercial counterparts in terms of gate counts. The temptation of commercial SRAM-based FPGAs over even the largest radiation tolerant devices is that they can be reprogrammed, perhaps decreasing development costs and increasing mission flexibility. The disadvantage of course is that they can be reprogrammed randomly by SEE. In addition, however, powerful proprietary (so-called intellectual property, or IP) cores have been integrated with the basic FPGA architecture—e.g. Processor cores in the Xilinx Virtex IV FX-60. [10], [11]

- 5) Optoelectronics, Sensors and Detectors: At the boundary where electronics meets materials science, band-gap engineered semiconductors and other detector materials play a crucial role for some missions. Their radiation response however is not always well understood. [12], [13], [14] However, even relatively mundane imagers, light sources can pose risks from both single-event effects and degradation mechanisms. The most advanced parts available in this category are either commercial or custom parts. For the former, no thought is usually given to radiation performance, while for the latter, the radiation performance may not be known in advance.

In many cases, it will be difficult to develop a system-level hardening solution without compromising the very advantages that make the component or technology desirable in the first place, and it may be better to pursue an RHBD approach like those discussed previously by Mike Alles. However, for some components and some applications a hardened ASIC, FPGA or even circuit approach will not be practical, and there will be no solution but to tailor the system so that the part can meet its requirements. Indeed, system-level hardening can be quite effective, in some cases yielding a system harder than would be possible fabricated purely from radiationhardened components with no system-level hardening.

#### 1.2 Overview of the system-level hardening process

Since system-level radiation hardening involves working closely with both system engineers and designers to achieve requirements, it is useful to understand the systemengineering perspective. The NASA Systems Engineering handbook defines a system as "a set of interrelated components that interact with one another in an organized fashion toward a common purpose" [15]. The common purpose of the system is captured in the mission requirements. In a space environment, a system faces a variety of radiation threats that could disrupt the organized interaction of the components and prevent the system from fulfilling its purpose. To prevent this, we must first carefully select components that meet their application requirements. For those components that are in danger of failing to meet requirements, we must tailor their interactions with the environment and within the system so that radiation threats are mitigated.

The system-engineering approach to dealing with hazards can be broken down into a deceptively simple three-step process [15] whose steps are:

- 1) Identify the threat

- 2) Evaluate the threat.

- 3) Mitigate the threat.

Achieving adequate reliability may require several iterations of steps 2 and 3, along with evaluation of the unintended consequences of any mitigation. Moreover, steps 2 and 3 are interdependent: A cursory evaluation of the threat may indicate that the application requires extensive mitigation that would be seen unnecessary given a thorough evaluation. Likewise, if our system incorporates mitigation from the beginning, we may be able to get by with a relatively simple validation test, rather than an expensive, extended threat evaluation. Since there may be no unique solution to this interdependent

problem, selection will usually be governed by the need to meet application requirements at minimum cost.

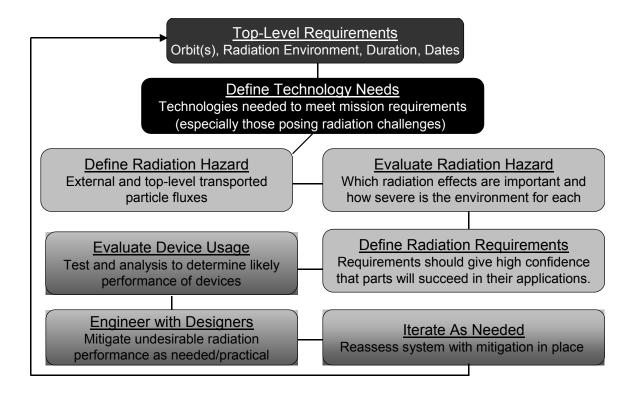

The NASA approach to radiation hardness assurance (see Figure 1-2) is compatible with this system approach. It begins by assessing the radiation threats and their severity for the mission environment. It then examines how the technologies needed for the mission will be affected by these radiation threats. Finally, the radiation engineer, designers, system engineers and other affected parties cooperate to develop mitigation strategies to ensure that the radiation threats do not impact mission requirements.[16] NASA's RHA strategy explicitly emphasizes the iterative and cooperative nature of the process—especially when it comes to mitigating undesirable radiation performance. For system-level hardening, we can assume that we already understand the radiation hazard and that a critical component is at risk of failing its radiation requirements. This means that we will be spending most of our time in the shaded boxes—that is, the boxes titled "Evaluate Device Usage," "Engineer with Designers," and "Iterate As Needed."

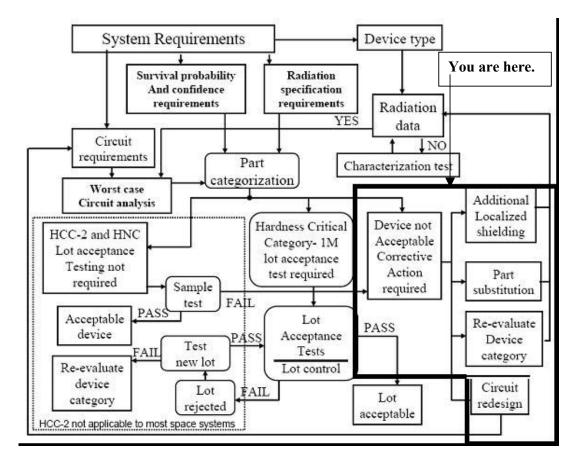

As an example, in the TID hardness assurance methodology of MIL-STD 814 (see Figure 1-3), we consider system-level mitigation only when a part fails requirements and winds up in the box labeled: "Device not Acceptable Corrective Action Required". Under normal circumstances, we might discard the marginal part and substitute one that is more likely to succeed.

However, sometimes a part is mission critical and there is no appropriate substitute, or if radiation analysis gets a late start, a problem part may already be integrated to the design and replacement would involve a very expensive and disruptive redesign effort. In such circumstances, the mission can:

- 1) Accept the risk of failure and use the part as is

- 2) Refine the testing and/or analysis to see if the part is likely to succeed under more realistic conditions.

- 3) Mitigate the risk of failure—in effect changing the requirements the part must meet while enabling the system to meet its requirements.

Testing, analysis and mitigation are time-consuming and expensive—in terms of project resources, schedule and—for mitigation—system performance. Even a few such parts can quickly break the bank for most projects.

Figure 1-2. NASA's approach to radiation hardness assurance (gray boxes) once toplevel mission requirements and the critical technologies needed to meet them have been defined (black boxes). System-level hardening activities occur mainly in the shaded boxes. (Adapted from reference 16.)

Figure 1-3. Most RHA issues can be resolved using Piece-Part Hardness Assurance Methodology outlined in figure 2 of MIL-HDBK 814[17] and adapted here. When a part falls into the Unacceptable category (block-bordered region) system-level hardening may be needed.

NASA's RHA approach also explicitly emphasizes development of radiation requirements. Top-level mission requirements may be difficult to apply directly to radiation threats, and so may require interpretation to guide designers, parts engineers and system engineers. Clear, verifiable and relevant radiation requirements are essential to determining whether system-level hardening is needed. We will deal with radiation-requirement generation in section 2 below.

The application environment—whether it is the orbit and mission duration for a satellite system or the near-interaction region for a particle physics experiment—determines the radiation environment. Performance requirements determine the technologies required for the mission. Knowing the technologies and the environment, we can identify the radiation threats to which the mission is susceptible. Indeed, many

severe threats can be avoided by screening out parts that pose *unnecessary* risk so that system-hardening efforts focus on the challenges that really lead to improved performance in achieving mission goals. References [1], [18], and Poivey [19] discuss the role of parts selection and screening in hardness assurance.

Most hardening is done by selecting parts that meet radiation requirements, by developing designs for ASIC or FPGA using hardening techniques, or by circuit designs to harden, for example, an analog system—solutions discussed in the sections of this short courses by Mike Alles, Fernanda Kastensmidt and Ben Blalock. However, when these techniques are not practical or fall short of the hardening required by the system, system-level hardening is a last line of defense to ensure system requirements are met..

Because the designation of the part as unacceptable is usually determined by testing or analysis at the piece-part level, piece-part hardness assurance serves as a departure point for our discussion of system-level hardening. A designation of "unacceptable" at the piece-part level is not necessarily a prediction of failure, but may instead indicate that we have insufficient information to predict with confidence that the part would fulfill its performance requirements. Since system-level mitigation can be costly, additional testing or analysis may be advisable if there is a reasonable chance that it will show that mitigation is not needed.

If the refined testing and analysis still show that mitigation is needed, then one must select a mitigation strategy that will meet requirements without bankrupting the project. Details of mitigation schemes have been covered in several short courses, including [20] for general discussions, and [21] and [22] for fault tolerance. In some cases, the difficulty may be selecting the best among several viable strategies. In other cases, there may be no viable strategy consistent with available resources, and the project will need to decide whether to relax requirements or make more resources available.

#### 2 WHEN DO WE MITIGATE?

Here we elaborate on a few concepts that will be useful in our discussions of systemlevel hardening. We first consider radiation requirements, since these define goals for hardening and the radiation environment. Next, since a part's acceptability is usually determined by radiation testing, we look at the uncertainties involved in radiation testing. Then, we look at the failure cost or severity, which scales the level of effort to be directed toward mitigating the radiation threat. Finally, we define radiation risk and related concepts—ways of combining the severity of a failure's consequences with the probability it will actually occur.

#### 2.1 Requirements generation and flowdown

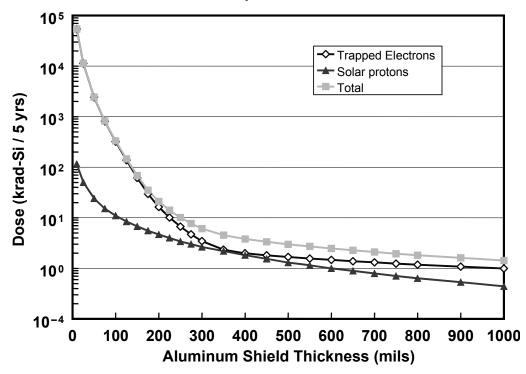

As mentioned above, requirements drive the cost and difficulty of any hardening effort. Clear, relevant, and verifiable requirements are essential to development of costeffective systems. Unfortunately, top-level requirements may be too vague to be verified without significant elaboration at lower levels. For instance, take the example of the Solar Dynamics Observatory (SDO), which is scheduled to begin a 5 year mission observing the Sun in 2009 (see Appendix in section 7). SDO's top-level survivability requirement for the Solar Dynamics Observatory might state:

#### The satellite shall operate for at least 5 years in a geostationary orbit.

While this requirement is acceptable at the top level, it is not clear what it implies for the radiation performance of components and systems on the spacecraft, and it cannot be verified until the spacecraft has in fact completed its five-year primary mission in the intended orbit. As such, one must derive from the top-level requirements, radiation requirements that support these requirements and that are verifiable in terms of radiation test data and analysis. At the level of the Mission Assurance Requirements (MAR) or the Parts Assurance Requirements (PAR), one derived requirement might state:

Builders shall use only parts that are immune to destructive single-event effects (SEE).

This gives clear direction in the selection of components for the mission. However, given that this requirement must be verified with test data, and that test data always have systematic and statistical uncertainties (e.g. part-to-part variation, Poisson errors in SEE error counts, etc.), we need to construct a verification requirement that gives us an operational definition of immunity to destructive SEE. For example:

For the purposes of part qualification, immunity to single-event effects shall be demonstrated if all of at least two samples of the part do not exhibit the effect when each is exposed to a fluence of  $10^7$  ions with an equivalent LET (where valid) of at least 75 MeVcm2/mg.

Note that the process moves from a very general requirement with clear relevance to achievement of mission goals via several steps to a verification requirement that can be clearly interpreted in terms of test data. At each step, there is an interpretation that must be justified as relevant. At the MAR/PAR level, the mission duration/survivability requirement is interpreted as a ban on the use of parts susceptible to destructive SEE. This clearly supports the intent of the top-level requirement. Although it could be challenged as too stringent for a 5-year mission, the fact that destructive SEE can occur any time makes a ban on their use prudent. The verification requirement interprets the term "immunity" in a way that can be demonstrated easily with SEE test data. Both the required fluence and minimum LET requirement could be challenged, but are defensible in terms of historic testing efforts for geostationary missions. Thus, the verification requirements due to its traceability to top-level mission requirements.

Similarly, for degradation mechanisms we may derive from the mission duration requirement above a requirement in the MAR:

All components shall perform their required functions with no system-level degradation after exposure to two times the mission total ionizing dose (TID).

Verification (and therefore any decision about the need for mitigation) relies on interpretation of test data—which we discuss next.

#### 2.2 Radiation Testing and Analysis: Errors and Inference

The complicated nature of radiation testing justifies a brief review of the types of errors that occur in different radiation tests, how these errors are handled and their implications for inferences about likely component performance. The radiation effects of concern here can be divided into two categories:

- 1) Single-event effects (SEE) result from the prompt effects of a strike by a single ionizing particle in a sensitive portion of the component.

- Cumulative effects such as displacement damage (DD) or damage due to total ionizing dose (TID) result from the gradual accumulation of damage by nonionizing or ionizing radiation, respectively.

Our goal in radiation testing is to bound the component's susceptibility to the effect so that we can determine whether the effect is likely to impact achievement of requirements. The bound will be a function of the mean radiation performance observed in the test and the errors on that result. As such, we need to understand the systematic and random errors that occur in radiation testing. We look first at TID and displacement damage, and then at SEE.

#### 2.2.1 Errors and inference for TID

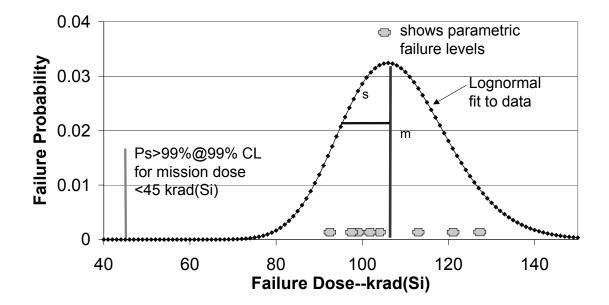

Because, TID hardness usually varies more than SEE from part-to-part and wafer diffusion lot to wafer diffusion lot and because lot qualification is done by destructive testing on a sample drawn from the lot, errors on TID results are normally dominated by sampling errors. The most general scheme for dealing with such errors—binomial sampling—makes no assumptions about the failure distribution, but requires sample sizes that are uneconomically large. Instead of taking this general approach, most TID performance [17] and so the failure distribution will be well behaved—that is, that the probability of having parts perform much worse than the mean performance will be small. This means that by increasing radiation design margin (RDM)—the ratio of the mean failure dose to that seen in the application—we diminish the probability the parts will fail to acceptably small levels. Unfortunately, not all failure distributions are well behaved (see figure 2-1), and if we merely assume a distribution is well behaved without requiring supporting evidence, we risk introducing systematic errors into the analysis. Still, this scheme usually works quite well.

TID data can be analyzed in two complementary ways to provide guidance to designers. The first way looks at the distribution of dose levels where different parts in the test sample meet some parametric or functional failure criterion. This type of distribution is useful for inferring what percentage of parts will fail at a given dose and for setting design margins. The second way of analyzing data looks at the distribution of parametric values or shifts for different parts in the test sample at a particular dose. This type of distribution gives designers information about how much degradation to design for in the system if we want more than a certain percentage of parts (say 99%) to be successful in that application. Both types of distributions are useful for system-level hardening.

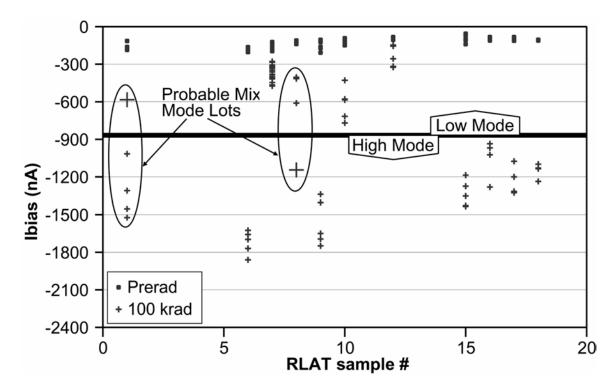

Figure 2-1. Distribution of Ibias for 11 lots of Analog Devices OP484 op amps shows considerable variation lot-to-lot and even within lots. Two of the lots even show evidence of bimodality, with most parts in one lot and one part (extra-large "plus" sign) straying into the other mode. This suggests that using design margin to increase hardness assurance may be a risky technique for these parts. (Adapted from reference 23.)

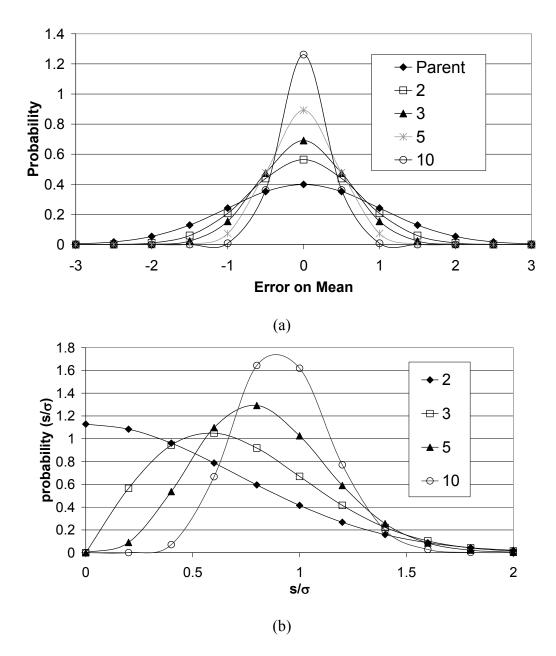

If we assume a particular form for the distribution (e.g. normal or more often lognormal) we can use our test sample to infer the parameters of the distribution. However, the smaller the test sample size, the more likely it is that our inferred distribution will be in error. For instance, figure 2-2 shows the distributions of how much the sample mean and standard deviation differ from the actual normal population mean and standard deviation as a function of sample size.

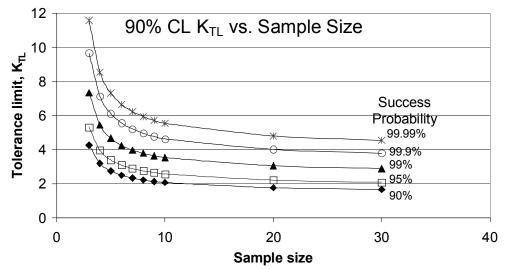

One solution to this dilemma is to use the one-sided tolerance limits, symbolized by  $K_{TL}$  to achieve a bounding estimate of the allowable dose or allowed degradation that guarantees success at the desired probability. In general the  $K_{TL}$  values are a function of the sample size *n*, the desired success probability  $P_s$  and the desired confidence level, CL—a measure of the assurance we require that our failure distribution will not be too optimistic. Figure 2-3 shows the  $K_{TL}$  values as a function of sample size for several desired success probabilities for the 90% CL. Values of  $K_{TL}$  are available in MIL-STD 814, or they can be calculated using Monte Carlo techniques. The advantage of the latter technique is that it can be used for any distribution form. The shape of the curves in Figure 2-3 is typical of how random errors often behave as data are added: When data are scarce, adding data has a large effect. However, for still more data, the curve approaches an asymptotic value.

As mentioned above, use of design margin for ill behaved failure distributions introduces systematic error into the analysis. While such systematic errors are not common, other types of systematic errors can affect TID testing. TID degradation can be quite application dependent. The fact that degradation can vary not just quantitatively, but qualitatively with dose rate—so-called enhanced low dose rate sensitivity (ELDRS) is well known. However bias conditions, temperature and other operating conditions can also bias experimental results. While it is impossible to have 100% fidelity to the application, the greater the fidelity of test conditions, the less the likelihood of systematic errors in the data.

Figure 2-2. Distributions of the sample mean a) and sample standard deviation b).

Figure 2-3. 90% CL one-sided tolerance limits, K<sub>TL</sub> vs. sample size for various P<sub>s</sub>.

In assessing whether mitigation is needed for a particular application, it is important to consider both random and systematic errors on TID data. In some cases, by testing more parts, one can reduce sampling errors sufficiently that mitigation may not be needed. In other cases, one may discover that data suggesting a part will succeed in an application may be systematically flawed, and it may be easier and more economical to mitigate TID degradation—e.g. by spot shielding—than to correct the error.

TID mitigation decisions can also be influenced by errors and biases in the analyses that estimate the dose a part is exposed to or circuit analyses that estimate the effect of a degradation on the application. Top-level TID estimates are often based on equivalent spherical shielding distributions, so TID estimates can be lowered significantly by more detailed sector analyses or Monte Carlo programs such as NOVICE.[24] On the other hand, if the spacecraft model—usually a sophisticated CAD file—given as input to a radiation transport program is flawed, the estimated doses will be also.

#### 2.2.2 Errors and Inference for Displacement Damage

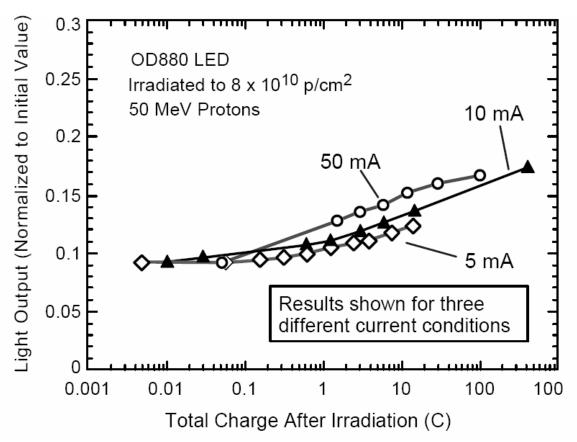

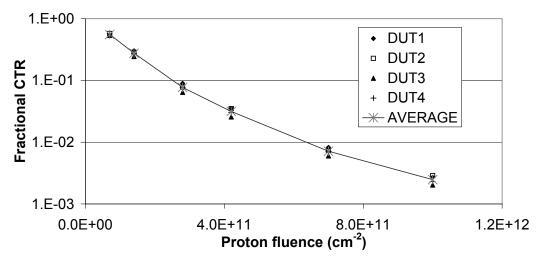

Although displacement damage performance generally varies less from lot to lot than does TID performance, the same statistical considerations and analyses apply. Moreover, for most part types, test results are also less application dependent. One exception is for optoelectronic devices, where annealing of damage is accelerated and increased in amphoterically doped LEDs by application of a forward voltage [25]. As with TID, estimates of displacement damage dose can be reduced significantly using more

sophisticated radiation transport techniques. However, because protons dominate displacement damage for electronics, adding sufficient shielding to significantly reduce displacement damage may add a lot of mass to the system.

#### 2.2.3 Errors and Inference for SEE

Although SEE rates can vary from lot to lot for commercial devices, this variability is much less important than for TID. Instead, random errors on SEE cross sections fluctuate about a mean value  $\mu$  according to the Poisson distribution:

$$P(n,\mu) = \frac{\mu^n}{n!} \exp(-\mu).$$

(2-1)

Percent errors due to Poisson fluctuations decrease as  $\mu^{-1/2}$ . Thus, as long as one can gather enough data, random errors can be reduced to the point where they are insignificant.

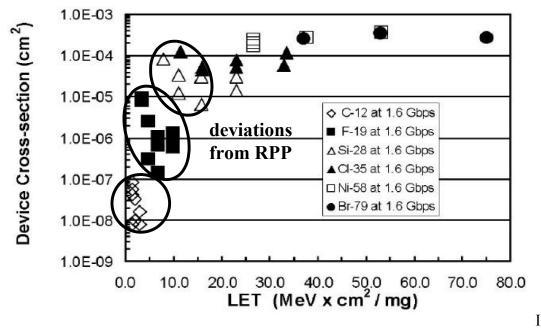

Systematic errors for SEE on the other hand can be pernicious, because they can bias experimental results in a particular direction and can be difficult to estimate. (See Figure 2-4.) In part, this is because the charge collection volume in the device under test (DUT) may deviate from the assumed rectangular parallelepiped. Also, the SEE cross section vs. LET curve may deviate systematically from the assumed Weibull form. Biases in radiation environment models constitute a third possible source of systematic errors.

Figure 2-4. The shallow trench isolation of SiGe HBTs coupled with the importance of charge collection by diffusion causes their charge collection volume to deviate significantly from a rectangular parallelepiped, resulting in violations of effective LET assumed for standard rate calculation methodologies. (Adapted from reference [26])

Reference [27] examined this problem, looking at the distributions of predicted to actual ratios of SEE rates by a variety of analysts for a variety of parts. The author determined that the canonical 2x uncertainty usually cited for SEE rates is a reasonable estimate of the systematic errors in rate calculation methods, but that estimates may be significantly worse depending on the part, the adequacy of the data and the procedure followed by the analyst. Unfortunately, it is likely that the development of technology in the past decade has resulted in significantly larger systematic errors, especially for some technologies [26].

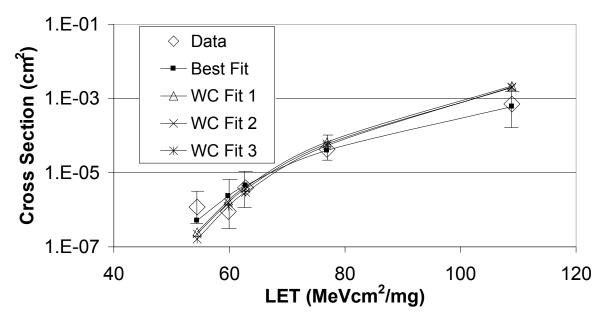

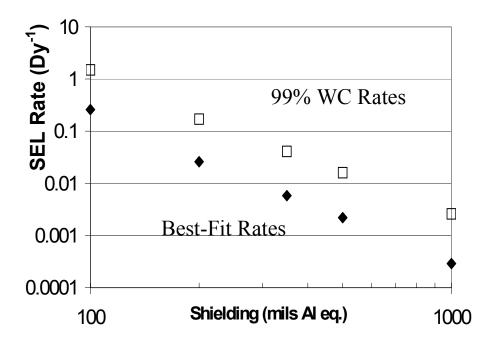

Usually these systematic uncertainties dominate the errors on SEE rates. The only exception occurs when SEE cross sections are based on very low event counts, as is often the case for destructive SEE. In this situation, a variety of fits may be consistent with data including error bars. For the SEL data in Figure 2-5, the 99% worst-case fits to the data yield error rates about 5 times worse than those for the best fit. Whether one chooses a conservative or a tight fit to the data may depend not just on one's understanding of the random and systematic errors on the data, but also on the consequences of the SEE if it occurred.

Figure 2-5, When SEE cross sections ( $\sigma$ ) are based on low event counts, the  $\sigma$  vs. LET curve can be fit by a broad range of Weibull curves if one includes error bars. For this SEL  $\sigma$  vs. LET curve for a 256 Mbit SDRAM at 85 °C, the resulting curves make a difference of about 5× for the SEL rate.

#### 2.3 Failure Cost and Severity

While engineers seek to avoid failure in any application, not all failures are of equal concern. Failures that result in a loss of mission objectives clearly merit greater level of effort than nuisance failures, and failures that could result in loss of life are of grave concern. One way of quantifying this difference is to look at the cost of the failure. Failure costs can be defined in terms of lost observing time for a science mission, dropped cell phone calls, data lost or fatalities. In terms of directing level of effort and comparing risks, it is easiest to define the failure cost monetarily. It should also be remembered that failures—especially those that make the news—have costs beyond the immediate loss of mission objectives, assets, etc. These may include loss of prestige, future business, and so on.

Estimating failure costs is a fairly involved effort. However, it can be very useful for efficient allocation of resources. It is here that the collaborative nature of radiation hardening is best illustrated, since the only way for a radiation specialist to understand the costs associated with an error or failure is by working with designers and system

engineers. The radiation engineer has an understanding of what a failure or error mode does at the device or component level. Designers usually have the best understanding of a system's functionality and will be able trace how the failure will affect it. Finally, system engineers will be best placed to understand how an error or failure mode will affect requirements. For this exercise it is essential that all involved understand the nature of the error or failure mode, its consequences from the part to the mission level and options for possible mitigation and recovery. One useful question to ask is: "If you knew with 100% certainty that this error/failure would occur the first day of the mission, what would you spend to stop it from happening." Then one can modify the question with the fault occurring midway through the mission, three-quarters of the way and so on. This gives an idea not only of the failure cost, but how it changes with time.

An alternative way of prioritizing hardening efforts is the concept of failure severity. MIL-STD 1629A defines severity as a relative measure of the consequences of a failure mode. Like cost, severity is defined in terms of the consequences of a failure. The advantage of severity is that it has a small number of broad categories, and reliability analyses often determine it as a matter of course. The Failure Modes Effects and Criticality Analysis (FMECA) is a very useful tool for identifying threats to system reliability, and the single-event effects criticality analysis (SEECA) can function similarly in SEE analysis.[28]

The NASA System Engineering Handbook defines 4 levels of criticality:

| Category I   | Catastrophic failure (possible death or system loss)                                                           |

|--------------|----------------------------------------------------------------------------------------------------------------|

| Category II  | Critical failure (possible major injury or system damage)                                                      |

| Category III | Major failure (possible minor injury or mission effectiveness degradation)                                     |

| Category IV  | Minor failure (requires system maintenance, but does not pose a hazard to personnel or mission effectiveness). |

MIL-STD 1629A defines severity levels as:

Category I catastrophic Category II critical Category III marginal Category IV minor. As with failure cost, failure severity must be determined in collaboration with designers and system engineers. Failure severity and failure cost can be related by assigning a dollar amount to each severity category—effectively scaling the level of effort to be directed toward mitigating a failure of a given severity category.

#### 2.4 Failure Risk and Criticality

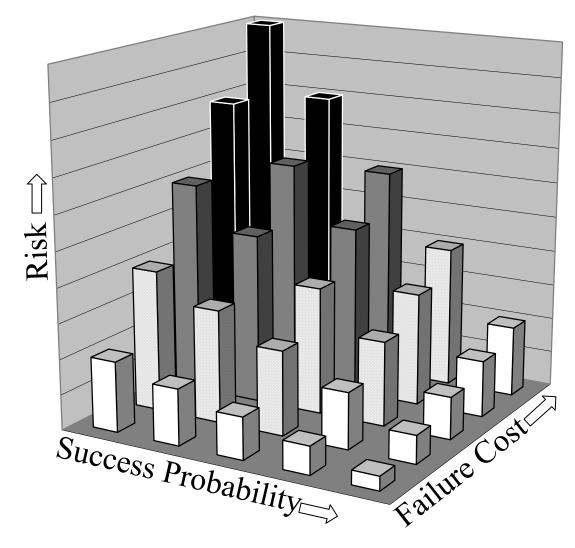

The failures of greatest concern are those with high severity/cost that are likely to happen. Failure criticality couples a failure severity with a probability of occurrence (See Figure 2-6.). While criticality is very useful for tracking system vulnerabilities, it can be difficult to compare different criticality categories: for example, is a Category II/high-probability failure a greater or lesser concern than a Category I/Low probability failure? The concept of failure risk,  $R_f$  combines failure cost— $C_f$ —and failure probability— $P_f$ —but in a quantitative (see Figure 2-7),

$$R_f = C_f P_f \tag{2-2}$$

More generally, both the probability and cost of failure may be functions of time, and the mission-integrated risk will be

$$R_f = \int C_f(t) x P_f(t) dt$$

(2-3)

| Severity<br>Probability | Category I<br>(Catastrophic) |                        | Category III<br>(Major) | Category IV<br>(Minor) |

|-------------------------|------------------------------|------------------------|-------------------------|------------------------|

| High Probability        | Very Critical                |                        |                         | Moderately<br>Critical |

| Moderate<br>Probability | Very Critical                |                        | Moderately<br>Critical  | Acceptable             |

| Low Probability         | Critical                     | Moderately<br>Critical | Acceptable              | Acceptable             |

Figure 2-6 Criticality reflects the level of concern posed by a failure (and thus scales the level of effort appropriate for its mitigation) by qualitatively combining failure probability  $P_f$  and failure severity.

The quantitative nature of the risk metric facilitates comparison of risks and prioritization of resources. Moreover, since we can assign a cost to each severity

category and severity is often determined for FMECA, much of the work is often done for us.

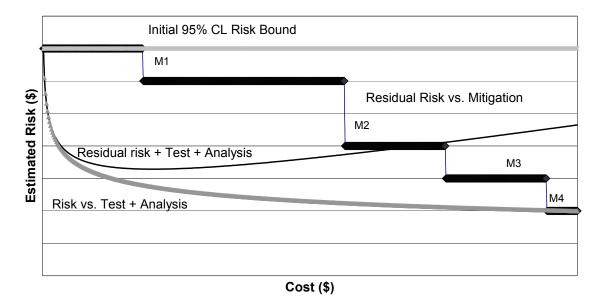

The risk metric can also be used to direct risk mitigation efforts by optimizing risk reduction per unit cost. One way to do this is to adopt the strategy that minimizes a new combined risk metric  $R_c$  that also reflects testing costs  $C_t$  and mitigation costs  $C_m$ :

$$R_c = R_f + C_t + C_m \tag{2-4}$$

and adopt the strategy that minimizes this metric. Just as the cost of failure may include intangible elements, the cost of mitigation should include reduced performance, reduced reliability and other factors as well as the actual cost of implementing the mitigation—all of which are determined collaboratively with designers and system engineers.

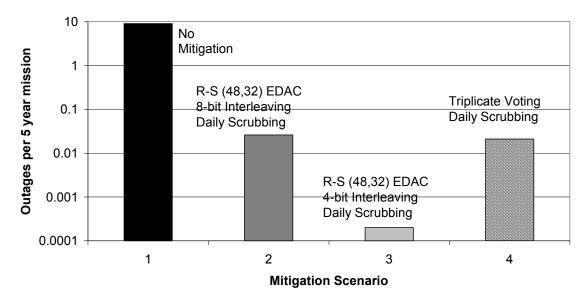

Figure 2-8 represents the decision process for mitigation schematically. Initially, we have little information about our probability of failure or its consequences, and so we have a high, though not unbounded, risk. (If nothing else, the risk is bounded by the cost of the mission.) As we begin to test and analyze our critical component, our estimated risk falls rapidly. At some point, however, risk reduction vs. testing/analysis curve begins to flatten, and the reduction in risk we get from additional testing or analysis is less than the cost of that effort. We can, however, still lower the risk by mitigation, and we apply mitigations M1, M2 and so on in decreasing order of cost-effectiveness (that is, risk reduction minus mitigation cost) until we meet requirements or until there are no more cost-effective mitigation strategies. In the next section, we look at the radiation effects in our system and how we can mitigate them.

Figure 2-7. Risk is the product of failure cost, Cf and failure probability Pf, and so reflects a quantitative measure the level of concern posed by a failure.

Figure 2-8. Schematic representation of tradeoffs between testing and analysis and mitigation.

#### **3** RADIATION EFFECTS AND THEIR MITIGATION

At the system level, we are mainly interested in the consequences of radiation effects and their mitigation. While the basic mechanisms responsible for those effects are very important for hardening at the device or circuit level, they matter at the system level only to the extent that they affect our design or suggest mitigation strategies. Discussions of basic mechanisms can be found in past Short Courses and the references therein.

For this very high-level approach, we first look at the types of effects we need to mitigate—dividing the universe of radiation effects into prompt—or single-event effects—and cumulative effects, or TID and displacement damage. We further divide SEE between destructive and nondestructive SEE. Destructive SEE tend to affect particular technologies—such as SEL in CMOS devices or single-event gate rupture (SEGR) in power MOSFETs. On the other hand, nondestructive SEE tend to affect a particular cell type, regardless of its technology—for example, SEU occur in bistable cells, while if the cell is not bistable, it will be prone to SET. TID and displacement damage susceptibility depend on details of the technology, but also on application conditions. Moreover, while rapid destructive—or functional—failures due to TID and displacement damage do occur in some devices, more usually, failure occurs after a period of gradual parametric and functional degradation.

The consequences of radiation effects also depend on the application to varying degrees. Consequences of destructive SEE are usually unambiguous—loss of functionality or if the system contains redundant functionality, decreased reliability. Consequences of nondestructive SEE tend to be much more application dependent. An SET may have no effect if it is not captured by a bistable device downstream. The consequences of an SEU depend on which bit flopped and when. Usually there is little ambiguity when a SEFI occurs, since by its nature, a SEFI disrupts normal device functionality. Still, the consequences may be very different depending on when the SEFI occurs. TID and DD degradation may initially have no system-level consequences, as long as parametric degradation does not exceed system tolerances. Eventually, however, parametric degradation results in performance degradation and eventual functional failure.

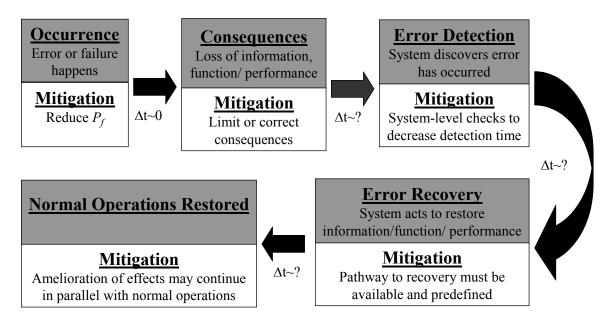

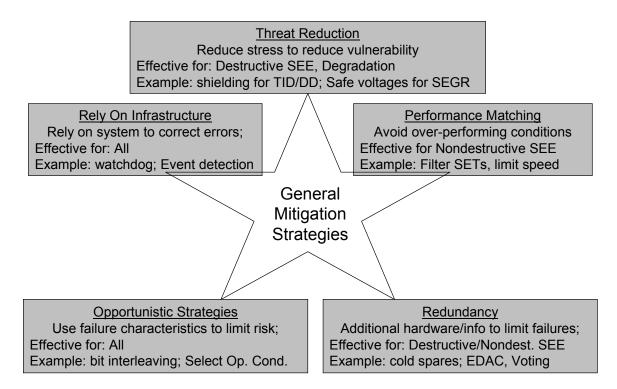

In order to understand how various system mitigation techniques work, it is helpful to understand how the system responds to an error, failure or degradation. Regardless of the cause, at the system level, what is observed is anomalous function. Figure 3-1 illustrates the steps that occur in response to an anomaly (grey rectangles) and the mitigation strategies that can be helpful for each stage (white rectangles). Of course the most effective strategy is to keep the error from occurring by reducing its probability of occurrence. However, four out of five stages have to do with anomaly recovery, and the effective mitigation involves limiting the consequences or speeding that recovery. Error consequences can be limited by correction (e.g. EDAC or voting) or by isolation of the error (e.g. by preventing execution of a command prior to its validation). Error detection can be facilitated by such techniques as overcurrent sensing for SEL and watchdog timers and error counting to discover SEFIs. Error recovery and restoration of normal operations are facilitated by having a sufficient understanding of system error modes that a recovery plan can be implemented automatically by software or quickly by ground operations. Finally, even after normal operations are restored, mitigation of anomaly consequences can continue.

Figure 3-1. Steps in the process of recovery from an anomaly.

#### 3.1 Radiation Effects and their Consequences

Here we discuss how radiation effects impact system operations—including reliability, functionality and performance. The purpose of the discussion is to give an idea of the types of consequences that will require mitigation. We begin by discussing destructive SEE, then nondestructive SEE and finally degradation mechanisms.

#### **3.2 Destructive Single-Event Effects**

The mechanisms of destructive SEE have been dealt with in previous short courses [29] and in the pages of the Transactions on Nuclear Science, most comprehensively and recently in reference [30]. Because destructive SEE susceptibility tends to be technology dependent, any device fabricated in a potentially vulnerable technology should be assumed vulnerable to the failure mechanism unless test data and/or design and validation demonstrate otherwise. Moreover, the degree of vulnerability cannot be determined without test data. Unfortunately, destructive SEE testing is difficult to carry out. Every data point may represent the destruction of an expensive microcircuit. Even if the destructive mechanism can be quenched (e.g. by detection and current limiting) prior to damaging the part, destructive mechanisms are at the very least very disruptive to the testing process. The result is that destructive SEE cross section estimations are often based on more limited data and subject to greater systematic errors than those for nondestructive SEE. In addition, there may be other complicating factors. A device that exhibits SEL may in fact be susceptible to multiple SEL modes—some of which are destructive while others are not. A common nondestructive mode can even mask a rare destructive mode. Such was the case for the XA-1 ASIC used on NASA's SWIFT gamma-ray burst telescope, which exhibited nondestructive SEL at LET~8 MeVcm2/mg with a saturated cross section of  $5 \times 10^{-3}$  cm<sup>2</sup>.[31] However, at high LET, roughly one out of 30 SELs was found to be destructive. Given the 256 (128 primary and 128 redundant) XA1 ASICs being flown, the SEL threat was real, and the project had to implement mitigation (See below.)

Rate calculation for destructive SEE may also be subject to greater uncertainties than for nondestructive SEE. Cross sections for SEL and SEGR have been shown to depend on ion energy/range as well as LET, and effective LET is invalid for single-event gate rupture (SEGR) and single-event burnout (SEB) and related phenomena. As we will

IV-30

discuss below, all of these factors argue for a conservative approach when deciding whether to use a device susceptible to destructive SEE and whether system-level mitigation is required for such a device.

Most destructive SEE render a single part inoperable, although for stuck bits or single-event dielectric rupture, only a portion of the part is rendered inoperable. Specific radiation-induced failure modes encountered in microelectronic components are discussed below.

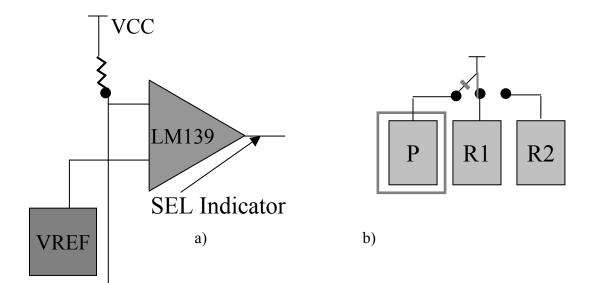

#### 3.2.1 Single-event latchup (SEL)

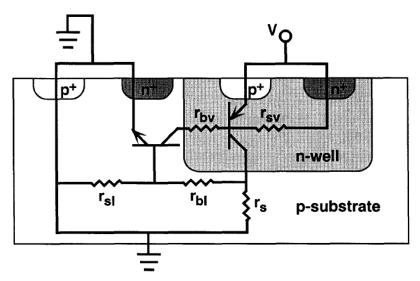

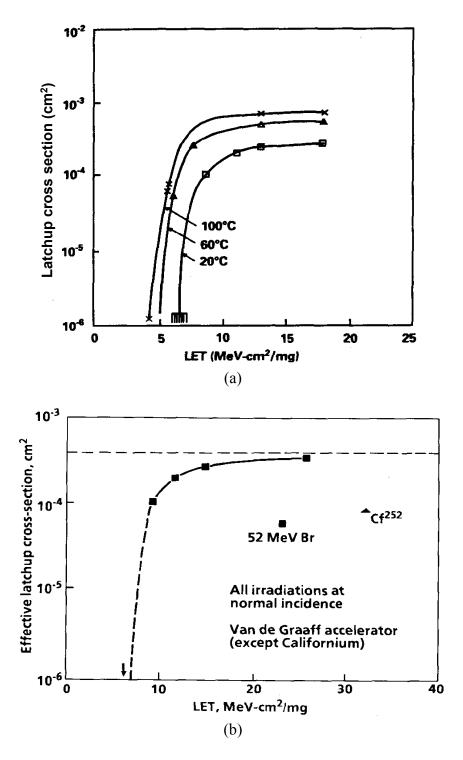

A *pnpn* structure in CMOS is equivalent to a bipolar silicn-controlled rectifier (SCR) that exhibit a regenerative latchup mechanism. (See Figure 3-2) Once triggered, this regenerative mechanism can amplify currents to the point where the device fails due to thermal overstress. Although SEL has been observed only in CMOS technologies, SEL is inherently a bipolar phenomenon that depends critically on the bipolar gains of parasitic bipolar junctions implicit in *pnpn* structures. As a result, SEL is exacerbated at high temperatures (Figure 3-3a) [32], [33]. Also, the parasitic structures inherently depend on substrate characteristics, so cross sections depend on ion energy and range, not just on an ion's LET [34], [35]. (See Figure 3-3b)

Protons and neutrons can initiate SEL as well as heavy ions. Recent in-depth investigations have shown that at least for some technologies, proton-induced SEL susceptibilities can increase significantly with proton energies [36] and may be worst-case at grazing incidence (possibly due to nuclear inelastic scattering of heavy metals in the part itself) [37].

IV-31

Figure 3-2. a) The parasitic bipolar SEL susceptible structure and its equivalent circuit. (Adapted from reference [29])

Understanding the implications of SEL for a system is complicated by the fact that SEL is not invariably destructive. In some cases—so-called micro-latch events resulting in localized high current—devices sometimes even remain functional. In some cases, the SEL may involve the entire device, but current densities may not be high enough to damage the device. However, even here, the situation is complicated by the fact that a device remaining functional after SEL is not a guarantee that it has not suffered damage that would compromise its reliability.[38] Such latent damage can be very difficult to detect, especially in devices with multiple metallization layers. NASA has issued an advisory on best practice for testing for and detecting latent damage in SEL susceptible circuitry [39]. Investigations of possible latent damage are also described in references [40] and [41].

Figure 3-3. a) The parasitic bipolar nature of SEL means susceptibility depends critically on temperature (after reference [32]). b) Similarly, because the bipolar structure involves the substrate, cross section depends on ion energy and range as well as LET (after reference [34]). Low-energy ions give lower cross sections whether they come from accelerators (Br) or the fissioning of Cf-252.

Given the variety of SEL responses a part can exhibit, testing for SEL susceptibility can be quite complicated. From this very brief summary, the important issues for systemlevel hardening are:

- 1) Understanding of SEL test data and its errors and limitations is essential to making appropriate hardening decisions.

- 2) Investigating latent damage is critical, because mitigations that are effective for destructive SEL are very different from those used for nondestructive mechanisms.

- 3) SEL is a high-current mechanism, and detecting this high current is the easiest way to determine that an SEL has occurred. However, it may not work for microlatch or if several devices are sharing a single power source as in a package of stacked die.

- 4) SEL is exacerbated at high temperature, so it is important to that testing envelops worst-case operating temperatures. In some cases, if the operating temperature can be maintained below a critical level SEL susceptibility can be lowered to the point where it is negligible.

- 5) SEL testing needs to take place at worst-case conditions, including the highest application voltage and temperature, and sufficiently high-energy heavy-ions and protons (if needed).

- 6) Destructive SEL renders the affected die inoperable. Because it is not possible to predict the electrical properties of the failed part, it is recommended that any mitigation strategy should electrically isolate the failed part from the rest of the system.

#### 3.2.2 Single-Event Burnout (SEB)

Even when there is not a *pnpn* structure, an ion strike can turn on a real BJT or a parasitic BJT structure in a (usually) n-channel MOSFET. The resulting second-breakdown causes a high-current state and can cause thermal failure of the device [42]. One can initiate a SEB without necessarily destroying the device, so it is usually possible to gather sufficient statistics to reasonably bound SEB susceptibility for a transistor.

Discrete transistors are only vulnerable to SEB when they are in their nonconducting (or OFF) state, and only when applied voltages (VCE for a BJT or VDS and VGS for a power MOSFET) are outside of a so-called safe-operating region, which must be defined by testing. As a rule of thumb, radiation hardened MOSFETs with rated VDS < 200V have not been seen to fail at less than 30-35% of their rated VDS for VGS=0. However, commercial MOSFETs have failed as low as 22% of rated VDS.[43] Operating devices within their safe operating voltages is the only effective mitigation for SEB. Effective LET is invalid for SEB, so typical rate calculation methods do not work.

#### 3.2.3 Single-Event Gate Rupture (SEGR)

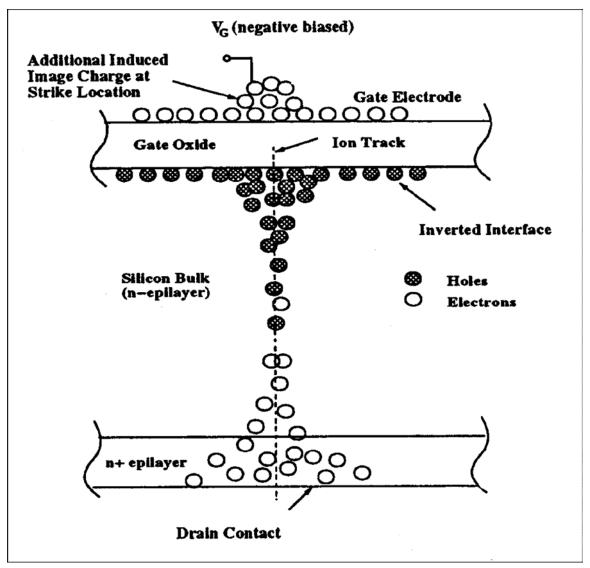

As with SEB, SEGR only affects discrete transistors (in this case power MOSFETs) when they are in their nonconductiong states (VGS  $\leq$  0V for n-channel devices or VGS  $\geq$  0V for p channel devices). Moreover, the effective mitigation strategy for SEGR is the same as that for SEB—derating of applied voltages to within empirically determined safe operating regions. The mechanism for SEGR is very different than that for SEB. In the case of SEGR, holes from the ion strike pile up under the gate, increasing the electric field across the MOSFET gate oxide to its dielectric breakdown point. (See Figure 3-4)

Figure 3-4. SEGR occurs when holes from the ion track aggregate under the gate oxide and increase the field across the oxide to the dielectric breakdown point. (Adapted from reference [44])

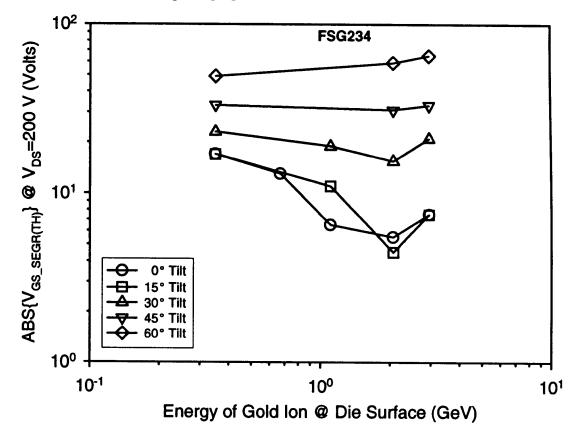

The resulting flow of current causes thermal failure of the gate oxide. As with SEL, SEGR testing is complicated by the fact a strip chart of gate current vs. ion fluence reveals so-called SEGR precursor events, where the leakage current through the gate increases in a stair-step fashion. These events represent localized breakdowns in the oxide and can result in latent damage. In addition, SEGR susceptibility depends on particle range/energy as well as LET (see figure 3-5). This means that commonly used SEE rate calculation methods will not work for estimating SEGR rates, although other methods have been investigated [46].

Figure 3-5 The complicated dependence of SEGR susceptibility on LET, ion energy and angle of incidence make it very difficult to calculate an accurate SEGR rate using conventional methods. (Adapted from reference [45])

3.2.4 Other Destructive SEE

**Single-Event Dielectric Rupture (SEDR)** was found to occur in one-time programmable antifuse-based FPGAs. The failure mode disables the affected gate and can cause partial loss of functionality while leaving most of the device functional. Rates for this failure mode were low, because the antifuse presents a small cross section and the

rupture follows an angular dependence similar to that for SEGR. Moreover, effective workarounds were found that mitigated reliability concerns and more recent generations of these devices seem to be more immune to such breakdowns [47].

**Second Breakdown** or burnout in bipolar devices has been known since 1994, when it was seen in a high-speed ECL devices [48]. More recently, it has been seen in several bipolar linear ICs [49],[50]. An angular dependence similar to SEGR and SEDR, and onset LET over 30 MeVcm<sup>2</sup>/mg ensure that rates for this failure mode seen to date are low. Moreover, the parts where this phenomenon has been seen are usually not so unique that another part immune to destructive failure could not be substituted if the rate were problematic.

**Single-Event Snapback (SES)**, like SEL is a regenerative effect that occurs in CMOS, but unlike SEL, it does not require a 4-layer *pnpn* structure [51]. SES occurs when an ion injects sufficient current into the drain junction of an n-MOS transistor resulting in avalanche multiplication. If the event is sustained by an external current source, the overcurrent can damage the device. SES has not yet emerged as a serious reliability concern. However, since it does not require a 4 layer structure, it is potentially a concern for SOI technologies [52]. Most hardening against SES is done at the process level, although as indicated above, current limiting can be effective in limiting damage due to this effect.

**Failures in FLASH Memories** have been seen to occur when the parts are operated in their WRITE or ERASE modes, even as these parts have exhibited significant immunity to all SEE when operated in their READ mode or when unbiased [53]. The failures during WRITE and ERASE are not surprising, since these modes use a charge pump to achieve the high voltages needed to program or erase the FLASH memory cells, and the failures are probably due to SEGR. For some parts, the onset of these errors occurs at sufficiently high LET that limited reprogramming would pose a relatively low risk.

**Stuck bits**—When an ion passes through a gate oxide of a transistor in a bistable cell (or in a pseudobistable Flash or DRAM memory cell), it may leave a dense local deposit of trapped charge that renders the cell unprogrammable [54]. Such a stuck bit may have an indeterminate output, or it may reside at its bleed-down value (0 or 1). At the system

level, it may look like a permanent SEU, and it reduces the effectiveness of mitigation for nondestructive SEE. To date, stuck bits have not occurred at rates that cause concern for most applications. Moreover, stuck bits usually anneal with time, so they are unlikely to accumulate to levels where they pose a serious concern.

#### 3.3 Nondestructive SEE

In contrast to destructive SEE tests, those for nondestructive SEE face no obstacle to gathering enough events at each LET value to make Poisson errors negligible. For this reason, systematic errors often determine the uncertainties for nondestructive SEE rate calculations. Another important thing to emphasize about nondestructive SEE is that the adjective nondestructive applies to the device in which the effect occurred, not necessarily the system in which that device resides. It is small comfort to know that if an SET puts a satellite into a flat spin, the device that initiated the disaster is still in good operating condition. Thus, it is important not only to understand the nature of the SEE, but also to understand it in the context of the component application. Consequences of nondestructive SEE often depend on application conditions, when the error occurs in the mission and so on. Nowhere is the application dependence more evident than when we consider single-event transients.

# 3.3.1 Single-Event Transients (SET)

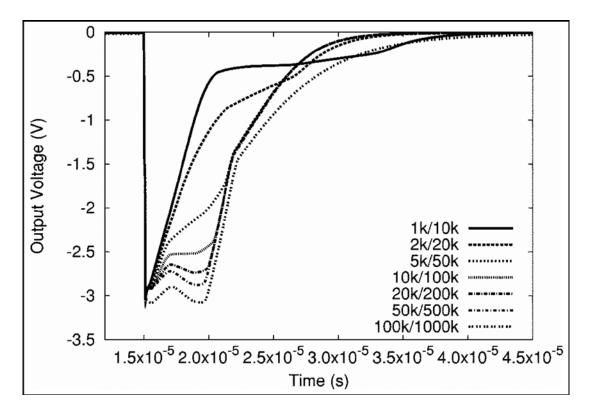

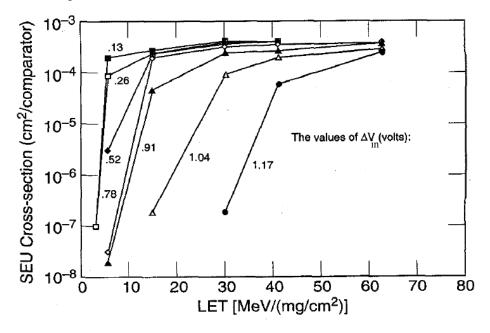

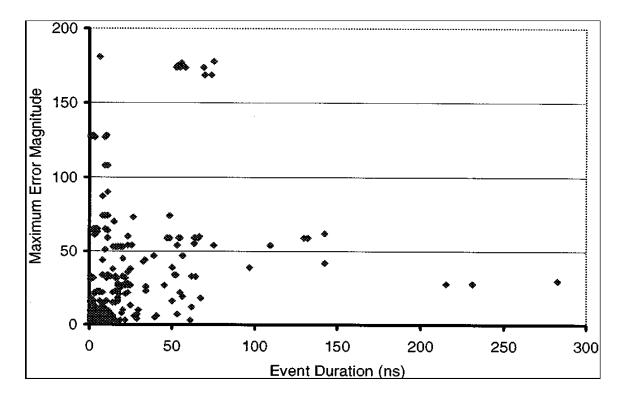

The effect of a transient is determined by its magnitude and duration (and possibly its waveform) and by whether a sensitive device downstream latches the transient and turns it into an upset at the system level. Transients are divided in analog SET (ASET)— usually associated with linear analog circuits—and digital SET (DSET), which are produced in digital circuits. ASET amplitudes and durations—especially in linear bipolar components—are often sensitive to application conditions including supply voltages, input voltages, loads and so on. (See Figure 3-6.) DSET are also produced with a range of durations and amplitudes, but tend to be shorter than ASET. Both types of transients tend to dissipate due to capacitive filtering, fanout and passage through several intermediate gates on the way to a bistable latch.

Whether the latch responds to the transient depends on how much the transient amplitude has decreased and when the transient occurs relative to clock edges[56]. For

this reason, it is important that the SET test setup have sufficient fidelity to the applications that circuit behavior can be accurately inferred. Because achieving such high test fidelity may require testing under many application conditions, SET testing at a heavy ion facility can be costly. Reference [57] discusses the more cost effective option of using a pulsed laser system to map out the application dependence of the SETs, with heavy-ion testing reserved for verification and determination and SET rate estimation.

Figure 3-6. SET durations for the LM124 depend not just on the gain, but on how the gain is achieved. Reference [55] showed that the width of transients from a particular transistor in the gain stage (Q9 specifically) of an LM124 in an inverting configuration depended on what resistance values were chosen to achieve the desired gain (here 10x) as well as the gain itself.

Since a transient's effect depends on the sensitivity of devices downstream, SETs remain a dynamic area of radiation effects research. The recent concern over DSET [58] and over-voltage conditions due to transients for deep submicron CMOS technologies are examples of new SET related threats [59]. As Ben Blalock discussed earlier in this volume, transients from a few linear bipolar devices last up to a millisecond [60]. In addition, what constitutes a long transient is relative. In very-high-speed technologies

such as SiGe and some high-speed A-to-D converters, transients may last only a few ns, but can corrupt dozens of data bits, giving rise to burst errors. Even ultra-fast devices like rf amplifiers may now need to be considered as a source of SET when they interface to very fast technologies. Each new generation of technology means we may need to reconsider our previous assumptions about potential SET related threats—and do so with no data from previous programs on which to base our conclusions.

For system mitigation of SETs, the important considerations are their short duration and localized effect, as well as the very application dependence that complicates analysis of transient effects. These characteristics suggest we can mitigate SETs by capacitive filtering, by resampling the output on timescales longer than transient durations, or by choosing our applied voltages, loads, etc. to minimize SET sensitivity.

#### 3.3.2 Single-event Upset (SEU)

SEU analysis is more deterministic than that for SET. Still, consequences of an SEU depend as much on the state of the system when the SEU occurs as they do on which bit upsets. In some cases, an SEU will have serious consequences only if it occurs during a narrow time window. For some applications, SEU may be correctable or have acceptable consequences if they occur at less than a critical rate, while in other applications a single bit flip could have serious effects.

Increasingly, because SET within a microcircuit may manifest as SEU, SEU rates are becoming more dependent on application conditions such as frequency, which makes it important to test at worst-case operating frequencies [61].

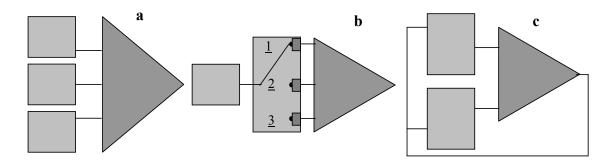

For mitigation purposes, SEU corrupt information stored in the device in which they occurs. Its effects, while persistent, are both local and correctable. However, increasing density due to scaling along with the burst errors mentioned above result in ever higher proportions of events that corrupt many bits simultaneously. More and more SEUs have consequences of multi-cell upsets (MCU).

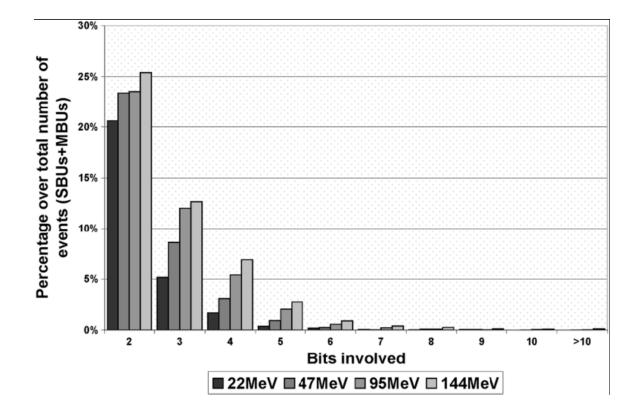

### 3.3.3 Multi-Cell and Multi-Bit Upsets (MCU and MBU)

Whether an SEU corrupts a single bit or multiple bits in a data word, the consequence is the same—corrupted data. MBU are mainly a concern because they are more difficult to mitigate. For example, MBU can undermine simple parity checks and other error

detection used in many command and control systems, just as they can defeat many error correction codes in system memory. Mitigating MBU requires much more sophisticated (and costly) mitigation than that used for SEU, so it is important to know whether MBU are possible in the system.

Although the continuing decrease in microcircuit feature sizes has resulted in increased occurrence of upsets that affect several adjacent cells—so-called MCU—many state-of-the-art memories now interleave bits from different words so that bits from the same word are never physically adjacent. To determine whether the separations used are sufficient, MBU tests must include worst-case conditions. For instance, unless one knows how the memory is organized, it is advisable to rotate the DUT about both the tilt and roll axes and to use angles as close to grazing incidence as possible. Moreover, since charge shared between adjacent cells increases with LET, the MBU cross section is even less likely to exhibit saturation than the SEU cross section.

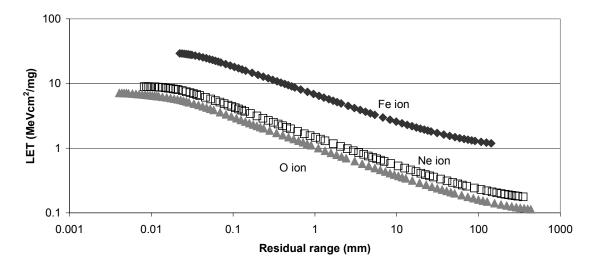

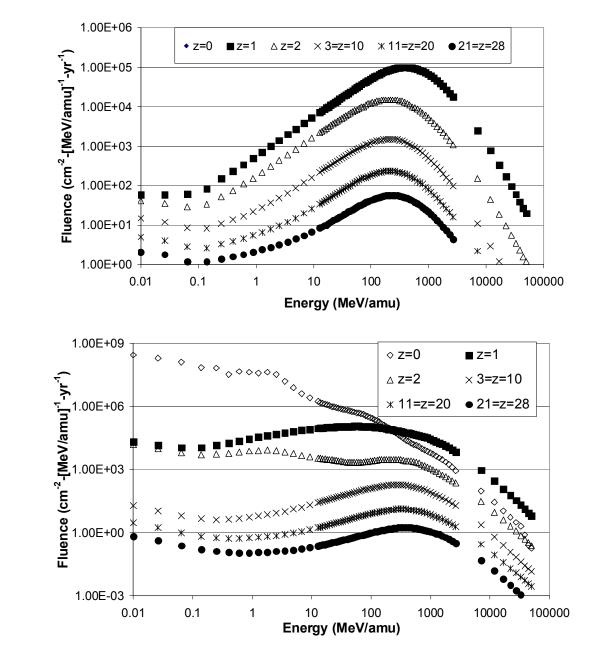

As device sizes continue to shrink, the question of how much separation is sufficient is under debate. Most accelerators produce ions with energies ranging from 10 to 40 MeV/amu and ranges up to a few hundred microns in silicon, while the GCR flux peaks at energies of about 1 GeV/amu and ranges on the order of centimeters in silicon. The higher energies of GCR protons and light ions produce higher energy recoil particles as well. The longer ranges and broader ionization tracks of these ions raise concern that terrestrial SEE testing could underestimate MBU cross sections. (See Figure 3-7) This is an area where modeling may be helpful if bit maps can be obtained from vendors or reverse engineered. Reference [62] reports on using a pulsed laser to reverse engineer the bit layout for a SRAM, which had a particularly a simple (and as it turns out, flawed) pattern of interleaving. Reference [63] discusses algorithms for finding the bit layout using broad-beam data, although such algorithms are laborious and computationally intensive. Although MBU require more sophisticated error correction schemes they still involve only a relatively small number of localized and physically adjacent bits.

Figure 3-7. Proportion of MCU corrupting from 2 to >10 bits for different neutron energies incident on an SRAM fabricated in 150 nm feature size technology. Bits were interleaved with bits from the same word separated by at least 8 columns. Although some upsets involved more than 8 bits, they never spanned more than 6 columns. (Adapted from Reference [64]

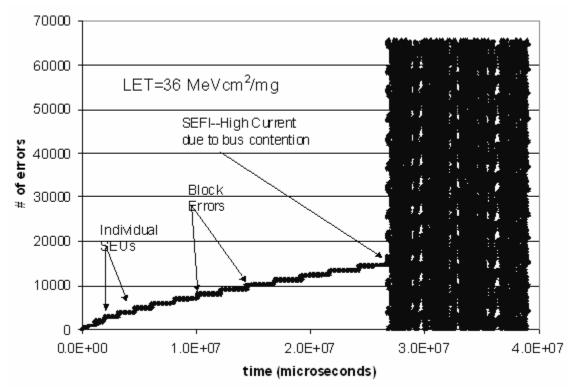

# 3.3.4 Single-Event Functional Interrupt (SEFI)