1

#### Are Current SEE Test Procedures Adequate for Modern Devices and Electronics Technologies?

#### Kenneth A. LaBel Co- Manager, NASA Electronic Parts and Packaging (NEPP) Program NASA/GSFC ken.label@nasa.gov 301-286-9936 http://nepp.nasa.gov

#### Lewis M. Cohn, Defense Threat Reduction Agency Ray Ladbury, NASA/GSFC

### **Outline of Presentation**

- Introduction and Background

- JEDEC Standard JESD57 brief summary of related guidance

- Considerations for additions to test planning process

- Beam-related characteristics

- Test parameters

- SEE Conditions

- Data Capture

- Destructive Events

- Discussion and Summary

#### **Disclaimer:**

This is not a comprehensive talk, but about considerations and thought processes

#### **Introduction and Background**

- At HEART 2007, we presented some of the burgeoning challenges associated with single event effect (SEE) testing of modern commercial memories

- Package, device complexity, test fixture, and data analysis issues were discussed

- "Complete" SEE Characterization would take

15years

- Qualification test costs have a >4x increase over the last decade (up from 3X of last year)

- In this talk, we continue to explore the roles of technology with an emphasis on the existing SEE Test Procedures and some of the concerns related to modern devices

- The primary objective of the briefing is to provide some overarching guidance concerning the many considerations involved in the formulation of a SEE test plan provided in a "Checklist" format.

- We note that there is no such thing as a complete test check list and that the best approach is to develop a flexible test plan that takes into account the device type and functions, the device technology, circuit and package design, and, of course, test facility and beam characteristics

http://www.flash-screen.com/free-wallpaper chicken-little-movie-wallpaper\_5795.html

### JESD57 – A Starting Point

- JEDEC JESD57 is the prime test standard utilized within the US for heavy ion SEE testing

- Developed in the early and mid '90s, it provides a reasonable starting base for planning SEE tests

- However, many new SEE-related considerations have forced us to consider some of the advice provided in JESD57. For example:

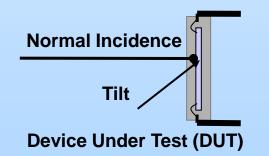

- Section 3.1.2.1: "The beam angle is normally limited to a maximum of 60 degrees...'

- This doesn't require that you test to 60 degrees, just a recommended normal limit. Multiple results showing differing sensitivities at higher angles has made angular work a requirement for some technologies.

- No discussion is present on asymmetric angular effects (i.e., tilting in both directions as well as changing the role of the device sample to the incident beam) stemming from technology and circuit layout

## NASA

### **SEE Test Guidance**

- Given the rapidly changing nature of both technology and the related SEE issues being discovered, it would be nearly impossible to create up-to-date test standards in a timely fashion

- The approach presented herein is to utilize a "checklist" in conjunction with SEE Test Standards for ensuring adequate radiation hardness assurance (RHA) is being met

- The following charts shall provide a look at selected checklist entries for digital electronics

- We note that this is NOT an attempt at presenting a complete list given both the length of this talk and the rapid discovery of new "challenges"

- But first, an example...

## Example: "Scrubbing" a Large Memory

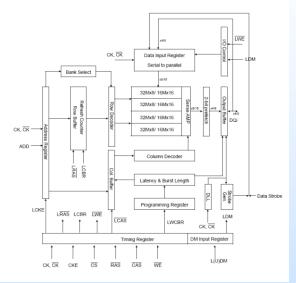

- Modern state-of-the-art memories now have greater than 1 Gb worth of storage cells

- A typical dynamic test flow might look like

- Write a test pattern to the entire device

- Verify the pattern

- Turn the beam on

- Perform a read compare, capture/count error, correct error (read-modify write) for the address space

- Repeat

- So what's wrong with this picture?

- Cycle time can be on the order of a minute for all address

- Missed errors

- Reverse bit-flips (i.e., flips back to correct state)

- SEFIs can occur masking bit errors

- All events are difficult to timetag when taking a minute to cycle through

- Important for determining SEFI rates or MBUs

- Implication is that the particle flux rate must be very slow to avoid false data and improve data capture statistics

### **Beam-related Characteristics - 1**

| Category | Test<br>Consideration | Description                                                                                                                                                    | Rationale or<br>Consideration                                                                                                                                                                                                                                                     |

|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU      | Energy dependence     | Test with same effective LET<br>with differing ions and energy                                                                                                 | LET equivalence and cosine<br>theta rule ineffective;<br>increasing role of<br>secondaries for scaled<br>technologies for low LET &<br>high energy particles;<br>Increasing impact of charge<br>sharing between critical<br>UDSM IC nodes causing<br>upsets in SEU "hard" devices |

| SEE      | Ion Range             | Ion range must be sufficient to reach sensitive volume/area at all test angles and ions used.                                                                  | Bragg peak effects as well as<br>metalization/package<br>materials add uncertainties                                                                                                                                                                                              |

| SEU      | Beam incidence        | Vary tilt and roll (board rotate)<br>to determine particle path<br>MBU effects and cell<br>symmetry; Angle range from<br>perpendicular to grazing<br>desirable | Transistors and cells are not<br>symmetric and need to be<br>irradiated at multiple angles;<br>Test can be done at limited<br>LETs for "calibration";<br>Increasing impact of charge<br>sharing between critical<br>scaled IC nodes causing<br>upsets in SEU "hard" devices       |

Presented by Kenneth A. LaBel at the 2008 Hardened Electronics and Radiation Technology (HEART), March 31 to April 4, 2008 in Colorado Springs, CO.

#### **Beam-related Characteristics - 2**

| Category | Test<br>Consideration    | Description                                                                                                                                                    | Rationale or<br>Consideration                                                                                                                                                                              |

|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU      | Flux rate                | Keeping the number of<br>particles per second<br>"tractable"                                                                                                   | Caveat is to ensure particle<br>interarrival time minimizes<br>probability of two particles<br>causing two events that look<br>like MBU between event<br>capture or that SEFIs don't<br>mask other events. |

| SEE      | Total dose<br>dependence | TID can affect SEE response.<br>Test matrix considers tracking<br>TID levels.                                                                                  | If known, do not accumulate<br>more than 80% of TID<br>tolerance of device during<br>SEE testing. If not known,<br>monitor DUT for evidence of<br>parametric degradation.                                  |

| SEE      | Displacement<br>damage   | Heavy-ion fluxes are usually<br>too low to cause significant<br>displacement damage.<br>However, it can be a<br>significant interference in<br>proton testing. | If known, do not accumulate<br>more than 80% of DD<br>tolerance of device during<br>SEE testing. If not known,<br>monitor DUT for evidence of<br>parametric degradation.                                   |

#### **Test Set Parameters**

| Category | Test Consideration                           | Description                                                                                                                                    | Rationale or Consideration                                                                                                                                                                      |

|----------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU      | Temperature                                  | Room temp - nominal; cryo is separate consideration                                                                                            |                                                                                                                                                                                                 |

| SEU      | Power supply voltage                         | Nominal; Nominal minus 5 to 10%<br>(pending device type/specs)                                                                                 |                                                                                                                                                                                                 |

| SEU      | Memory or shift<br>register test<br>patterns | Various: all 0, all 1, checkerboard,<br>inverse checkerboard, PRN                                                                              | Determine worst-case and nominal<br>SEU sensitivities of cell<br>storage symmetry. Use worst-<br>case where appropriate for<br>majority of testing. Column and<br>row striping may be required. |

| SEU      | DSET Potential                               | Various operating speeds and<br>voltage sensitivities: static,<br>min, max, nominal, derated                                                   | Determine test required to look<br>for propagation of transients to<br>digital logic or cell. Includes<br>clock frequency effects,<br>operating voltage sensitivity<br>and clock hits           |

| SEU      | Current monitoring                           | Strip charting of power<br>supply(ies) current<br>consumption required.                                                                        | Resolution and frequency of<br>measurement should be<br>considered.                                                                                                                             |

| SEU      | Operating modes                              | Devices can have high<br>number of operating modes:<br>try to determine a subset of<br>interest for worst-case or use<br>application-specific. | Data can vary from mode to mode,<br>so be careful.                                                                                                                                              |

## NASA

### **SEE Conditions - 1**

| Category | Test<br>Consideration | Description                                                                                                                                               | Rationale or<br>Consideration                                                                                                                                                                                      |

|----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU      | MBUs - general        | Single particle, multiple cell<br>events                                                                                                                  | Caveat is to ensure particle<br>interarrival time<br>minimizes probability of<br>two particles causing two<br>events that look like MBU<br>between event capture<br>Obtain physical to logical<br>bit map for SRAM |

| SEU      | Block errors          | Page, column, row or partial<br>errors of both                                                                                                            | Must determine if recovery is<br>possible without power<br>cycle (mode register<br>refresh, reload controls,<br>reload, data,). Real-time<br>determination?                                                        |

| SEU      | MBUs - angular        | Vary tilt and roll (board rotate)<br>to determine particle path<br>MBU effects and cell<br>symmetry; Angles from<br>perpendicular to grazing<br>desirable | Transistors and cells are not<br>symmetric and need to be<br>irradiated at multiple<br>angles; Test can be done<br>at limited LETs as<br>"research"                                                                |

# NASA

### **SEE Conditions - 2**

| Category | Test<br>Consideration | Description                                                                                                                                                                        | Rationale or<br>Consideration                                                                                                                                 |

|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU      | SEFI                  | Tests should take into<br>account potential<br>SEFIs that may<br>manifest (control,<br>test, or mode hit).<br>This includes<br>determining test<br>fluences when events<br>happen. | Determining of how to<br>clear SEFI (re-write<br>mode register, soft<br>reset, power cycle,<br>etc) is important to<br>determine. Real-time<br>determination? |

| SEE      | Stuck Bits            | Need to determine if<br>error is occurring at<br>same location all the<br>time. Re-writes and<br>clears use.                                                                       | If microdose, annealing<br>can occur to remove<br>event.                                                                                                      |

#### **Data Capture**

| Category | Test Consideration               | Description                                                                                                       | Rationale or Consideration                                                                                                                                   |

|----------|----------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEE      | Statistics                       | Fluence levels should be high<br>enough to get statistical<br>significance of data without<br>fear of beam pileup | Consider higher fluence level<br>to look for small probability<br>events such as in control<br>logic.                                                        |

| SEE      | Real-time error<br>determination | Need to observe any non-<br>traditional events                                                                    |                                                                                                                                                              |

| SEFI     | Current monitoring               | Strip charting of power supply(ies)<br>current consumption required.                                              | Resolution and frequency of<br>measurement should be<br>considered. SEFIs sometimes<br>show as a current draw<br>change.                                     |

|          | Time-tagging                     | A requirement to look at single<br>particle, multiple events or to<br>post-process for block or<br>SEFIs.         | Caveat: For a memory array, all<br>cells can be considered to<br>have the same time tags<br>during one read cycle of<br>array. See also flux rate<br>issues. |

#### **Destructive**

| Category     | Test<br>Consideration   | Description                                                                                         | Rationale or Consideration                                                                                                                                                                                     |

|--------------|-------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL          | Temperature             | Worst-case for SEL is high-temp.<br>70-80C for COTS; 100-125C for<br>Military                       | SEU data often taken at same<br>time, but not required (i.e.,<br>biased device with functional<br>check okay)                                                                                                  |

| SEL          | Power supply<br>voltage | Nominal plus 5 or 10% (pending device type/specs)                                                   | Beware of confusing SEFI mode<br>current changes with "non-<br>destructive" SEL. Latent<br>damage should also be<br>considered. Also, ensure power<br>rail is stiff and does not sag<br>with increased current |

| SEB/<br>SEGR | Temperature             | Data is <i>ambivalent</i> on high/low<br>temp testing- matters for SEB &<br>not for SEGR in general | Consider as part of SEL test<br>using high temp, high Vdd                                                                                                                                                      |

| SEGR/<br>SEB | Ion Range               | Ion range must be sufficient to reach sensitive volume/area for all ions used.                      | Bragg peak effects as well as<br>metalization/package materials<br>and depth of sensitive volume<br>add uncertainties                                                                                          |

#### **Destructive**

| Category     | Test<br>Consideration                             | Description                                                                                                       | Rationale or Consideration                                                                                                               |

|--------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| SEB/<br>SEGR | Power supply voltage                              | Vdd max or application plus 10%                                                                                   | Can also be a concern in non-<br>power devices.                                                                                          |

| SEL          | Current<br>monitoring                             | Strip charting of power<br>supply(ies) current consumption<br>required.                                           | Resolution and frequency of<br>measurement should be<br>considered.                                                                      |

| SEL          | Peak current                                      | Stop beam when occurring.<br>Current draw can increase with<br>time.                                              | Many SEL paths possible. Dwell<br>tests can be considered. May<br>not allow "runaway" levels if<br>SEU performance data still<br>needed. |

| SEL          | Power cycling                                     | Power supply should be<br>incrementally lowered to<br>determine holding voltage where<br>SEL is removed.          | SEL has been observed on < 1.25V devices.                                                                                                |

| Snapback     | Mainly an issue<br>in SEU<br>hardened SOI<br>NMOS | Snapback is a parasitic bipolar<br>regenerative. Vdd is nominal<br>+5/10%; WC temperature is high<br>temperature. | Can be initiated by TID so need<br>to ensure that this is not a<br>factor. Current limiting can be<br>considered.                        |

#### **Discussion and Summary**

- Believe it or not, this has been a simplistic look at starting a checklist for SEE testing

- Given a memory that has 68 operating modes, when a SEU occurs that changes the mode, just how do you determine what's going on?

- Laser and microbeam tests can help, but not easily for modern packaged devices

- Expanding this approach to other more complex devices such as ADCs or processors as well as analog devices should be considered

- The recommendation is to use the existing test standards as a starting point

- Just make your own checklist for the device/technology/issues being considered